【PC編】「2020.0921@★AVX2速い!★比較★SIMD命令、スレッド数」と「PCSX2@LINUX」と私

と題しまして小話を1つ。

ーーーーーーーーーーーーーーーーーーーーーーーーーーー

・12コア12スレッド(プラグインはAVX2で設定)

・12コア24スレッド(同上)

ーーーーーーーーーーーーーーーーーーーーーーーーーーー

でCPUの負荷のかかり方を比較してみました。

<12コア12スレッドの場合@libGSdx-avx2-1.0,0.soの場合>

時々、3,4個ほどのCPUの負荷が60%を越えてきますが

それ以外のCPUの負荷は30%〜40%の範囲に収まってます。

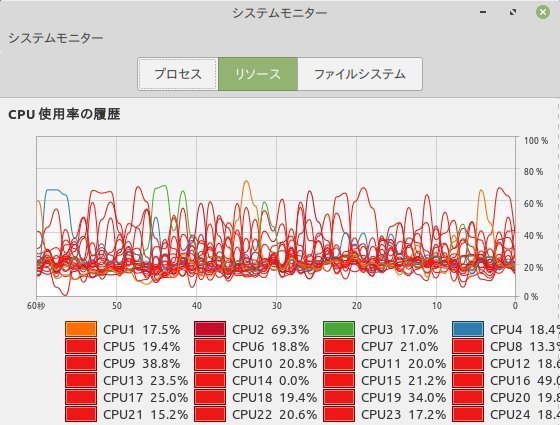

<12コア24スレッド@libGSdx-avx2-1.0,0.soの場合>

時々3,4程のCPUの負荷が60%越えてきますが、

その他のCPUの負荷は20%〜40%の範囲で収まってます。

負荷の波形の重なりが多い部分を見ると20%〜40%の範囲ですね。

<12コア24スレッド@libGSdx-intel-sse4-1.0,0.soの場合>

3,4個ほどCPUが60%越えてきますが、他は、大半が20%〜30%になってます。

<12コア24スレッド@libGSdx-1.1.0の場合>

3,4個ほどCPUが60%越えてきますが、他は、大半が20%〜30%になってます。

ただし、60%になってるCPUの時間がSSE4と比べるとえらく長い。

(1)グラフィックプラグインDLLによる負荷比較

プラグインの仕様としては、以下の感じです。

速度への影響をちょっと確認してみます。

グラフの中でCPU負荷が60%を越えてる

CPUの高負荷持続時間(グラフの山の長さ)を比較してみると

SSE2(20秒)、SSE4(10秒)、AVX2(3秒)で山の長さが短くなっています。

負荷の山の長さが短いというのは処理が早く終わるということ。

SIMD(Single Instruction MultipleData)仕様が

新しいものほど、処理が高速化し処理が早く終わため、

グラフの山の長さが短くなっていると推測します。

AVX2にすると、SSE2の6倍以上処理が

速くなることになります。

6倍以上速くなるってバカになりません。

結構効いてきますね。

(2)12スレッドと24スレッドでの負荷比較

グラフを見ると12スレッド版ではCPU負荷の中心が

30%〜40%に対して

24スレッド版は、20%〜30%の負荷になってます。

ハイパースレッディング(SMT)をON/OFFでは

ONすると最大3割ぐらいCPUの処理効率がUPすると

聞いたことがありますが、

負荷のグラフを見た範囲で、ざっくり、だいたい、

合ってると思います。

以下、各SIMD拡張命令の解説

(1)AVX2拡張命令

浮動小数点演算の演算幅がSSEの2倍の256ビットとなり、

1命令で8つの単精度浮動小数点演算もしくは

4つの倍精度浮動小数点演算を実行することができる。

また、命令デコード性能向上のため、

新しい命令フォーマット(VEXエンコーディング)が採用されている。

3 or 4オペランドの非破壊型命令もサポートするため、

レジスタ退避・復元処理の記述を省くことができる。

この非破壊型の命令フォーマットに関しては

従来の128ビット幅のSSE命令にも使うことができるため、

AVXに対応したプロセッサでは新規に導入された

256ビット命令を使わなくてもSIMD演算の性能が向上する可能性がある。

SSEが導入された際には専用の128ビットレジスタが新設されたが、

AVXの256ビットレジスタは下位の128ビットを既存のSSEレジスタと共有している[11]。

そのためSSE命令とAVX命令の間でのデータ交換は容易である。

ただし、256ビットのAVX命令と既存のSSE命令を混在させると、

SSE命令を実行する際にAVXレジスタの上位128ビットを退避する

というペナルティが発生するため、パフォーマンスが落ちる。

これを避けるためには、256ビット命令の実行後に

VZEROUPPER/VZEROALL命令を実行して明示的に

AVXレジスタの上位128ビットをクリアするか、

SSE命令をVEXエンコーディングを使ったものに置き換える必要がある。

上位128ビットを保持せずにゼロクリアするという挙動になっており、

AVXレジスタの部分的な書き換えが発生しないためである。

Sandy Bridgeでは当初のSSEの実装のように既存の128ビットの

演算器を使って2サイクルで実行するようなことはせず、

素直に乗算器や加算器などの演算器が256ビット幅に拡張されている[10]。

AVX2では、従来のSIMD整数演算命令が128ビットから256ビットに拡張されるのが

主な変更点であるが、要素ごとに独立したシフト量を設定できるシフト命令、

非連続なデータを並べ替えながらロードが可能なギャザー命令等の

128bit幅に留まっていたため、AVX2命令を多様する処理はあまり

高速化されていなかった。Zen2世代からは256bit幅になり処理速度が改善。

(2)SSE4拡張命令

※余り記載がありません。

★SSE4.1[編集]

45nm世代のCore 2のPenrynで搭載。47個の命令が追加になる。

★SSE4.2[編集]

Nehalemマイクロアーキテクチャ の第1世代Intel Core iで初めて実装された。

7個の命令を追加。SSE 4.2の追加命令は以下の通り。

String & Text New Instructions (STTNI)

<PCMPESTRI>

- PCMPESTRM

- PCMPISTRI

- PCMPISTRM

- PCMPGTQ

- Application Targeted Accelerators(ATA)

- CRC-32

- POPCNT -ビットが立っている数を数える

(3)SSE2拡張命令

SSE拡張命令は、Pentium IIIにはじめて実装された。追加された命令数は70[2]。

廉価製品のCeleronにおいても、その第三世代製品 Coppermine-128k より

具体的には64ビットの倍精度浮動小数点演算のサポート及び

制御機能の強化がなされた。

用いることを標準としたため、拡張命令ではなく基本命令として

SSE、SSE2が取り込まれている。

以下はハイパースレッディングに関するWIKIの解説です。

<ハイパースレッディングによる効果>

ハイパースレッディングの利点を以下に挙げる。

(1)マルチスレッドコードのサポートを改善する。

(2)多数のスレッドが同時に動作することを可能にする。

では・・また・・:_;)/